eFPGA IP — 灵活可重构逻辑加速内核

芯璐科技eFPGA IP面向SoC、MCU、AI加速器、工业控制与通信芯片场景,提供可重构、可升级、可迭代的逻辑算力层。基于芯璐科技自研的ArkAngel®工具链(AAEE),我们的eFPGA内核实现从架构探索 → RTL → 物理实现(GDSII)→ 数字化设计流程验证的全流程交付能力,在性能密度、可集成性与工具链体验方面处于行业领先。

核心优势

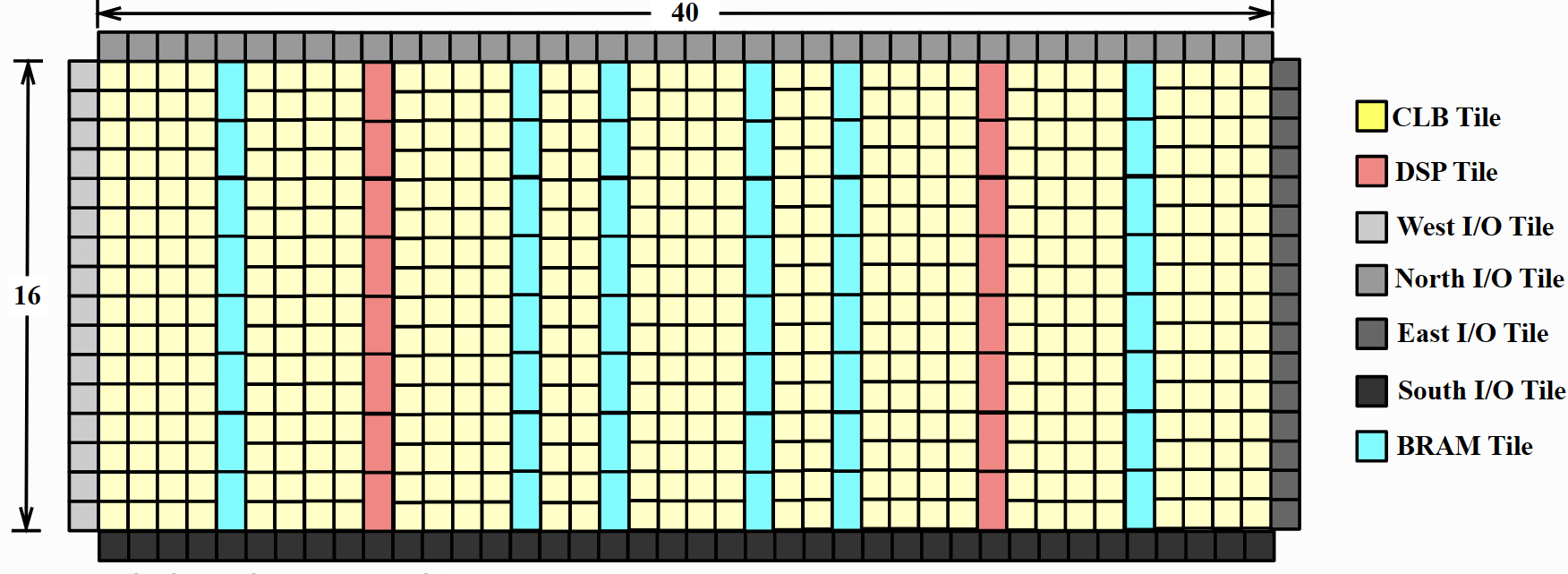

1. 高性能逻辑结构(LUT / FF / DSP-lite / BRAM)

· 可配置逻辑规模从数千至数百万LUT扩展

· 支持高密度可分布式存储

· LUT、FF、DSP-lite、BRAM 组合灵活,功耗极低

· 擅长控制与协议类、bit-level、流式处理场景

2. 超轻量、易集成的SoC级接口

· 支持 AXI、AHB、APB 等标准总线

· 灵活的 I/O 规划,可与封装/封测无缝衔接

· 支持低功耗、sleep/retention 、低功耗唤醒逻辑

3. 从RTL → GDSII的全流程IP内核交付

我们提供符合主流ASIC流片流程的数字化验证能力,包括:

· 综合(Logic Synthesis)自动 QoR 调优

– 面向性能/面积/功耗的多目标优化

– 基于工艺库(Lib)实现可量化 PPA 收敛

· Floorplan & Placement 支持

– eFPGA Fabric的分区/子阵列规划

– Boundary cell、Channel、高层路线结构定义

· Routing 与拥塞优化

– 可根据布通率预测进行局部结构优化

– 支持AI辅助的拥塞推断(ArkAngel® AE模型)

· 静态时序分析(STA)

– Setup/Hold/Clock gating全流程验证

– Multi-corner / Multi-mode

· 功耗估算(Power Analysis)

– 动态/静态功耗

– Fabric活动因子扫描

· 物理验证(DRC / LVS)

– 完整的版图设计规则校验

– 适配SMIC / TSMC等主流工艺

客户可根据项目需求选择:

· 软核Soft IP:可灵活调整架构与规模

· 硬核Hard IP:固定布局、性能确定、Tape-out 可直接使用

此能力已在 SMIC 40nm、TSMC 22nm 等主流工艺节点成功验证。

Rapid-Flex eFPGA IP已在多个行业场景中成功验证其可重构价值:

1. 电机控制 — 国产替代TI C2000

· 实现快速可编程 PWM、死区控制、过流/过压保护

· 可将电机算法/数字控制逻辑迁移至可重构逻辑

· 在工业伺服、电梯、电动工具、电动车控制器中具备显著灵活性

2. PMIC 电源管理 — eFPGA 作为可重构电源控制与时序引擎:将电源状态机、时序编排与保护逻辑以可编程逻辑实现

· 多路电源上电/下电管理:Power Sequencing、依赖关系控制、软启动/斜率控制、PG/FAULT 联动

· 可配置保护与容错:OVP/OCP/OTP、短路/欠压处理、故障隔离、自动恢复策略(按客户需求定制)

· 快速适配与可升级:门限/时序/策略无需改版主芯片,通过更新配置即可适配不同平台与客户需求

· 适用场景:PMIC、多路电源管理 SoC、工业与通信电源模块、服务器/边缘设备复杂供电系统

3. Edge AI轻量加速(传感器阵列)

· 事件驱动逻辑 / 特征提取 / bit-level 预处理

· 可升级、可修改的CNN前端处理模块

· 应用于智能安防、低功耗传感器集线器、AIoT

4. 高端射频 / 通信芯片

· 协议栈可重构:NR/5G、WiFi、专网通信

· Frame Parsing、CRC、调度逻辑可随协议更新升级

· 提供快速修订能力、适配不同地区标准

5. 图像处理ISP

· Sensor 接口处理(MIPI、DVP)

· 去噪、HDR 合成、Gamma、Auto-Exposure 辅助逻辑

· 可用于智能相机、车载影像、工业视觉

6. 智能网卡 / SmartNIC

· 可重构流表、Flow Steering、ACL / L4-L7 Parsing

· 可定制安全加速、加解密、报文分类

· 与 DPU/CPU深度协同,满足云和数据中心需求