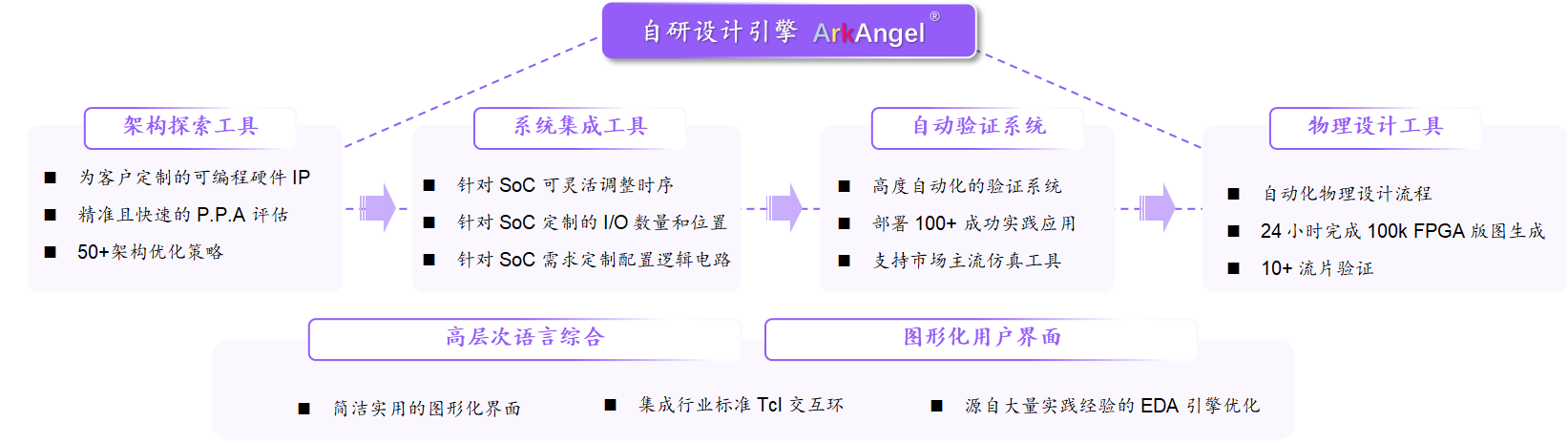

ArkAngel®芯璐eFPGA 架构探索与开发平台(EDA)

ArkAngel®是芯璐科技自研的全流程 eFPGA 架构设计与应用开发平台,面向希望在 SoC 中灵活集成可重构加速器的芯片企业。平台结合架构探索(Architecture Exploration)与应用开发(Application Development)两大核心能力,为客户提供从架构生成、资源规划、性能评估到Verilog-to-Bitstream开发的完整解决方案。

架构探索:AI 加持的敏捷eFPGA规划流程

ArkAngel® 通过可视化与自动化工具链,帮助设计者在短时间内完成eFPGA架构方案的快速迭代,包括:

· 资源规模配置:调整 LUT、寄存器、BRAM、DSP-lite等逻辑资源数量

· I/O 规划:灵活定义I/O数量与拓扑结构,便于SoC集成

· 快速 Floorplan:实时查看布局变化,评估资源密度与布线可行性

· PPA(性能/功耗/面积)快速评估

· AI 推断布通率(Routability)与拥塞趋势:基于大量内部项目数据生成预测模型

· 初步布线结构优化可带来约 20% 性能提升(典型案例)

借助ArkAngel®,设计者可在项目早期快速定型架构方案,大幅提升eFPGA的开发效率与可预测性。

应用开发:从 Verilog 到 Bitstream 的全链路工具链

ArkAngel® 支持完整的软件开发流程,使开发者能够在架构定型后高效完成应用构建:

1. 载入用户应用(Verilog)

2. 自动完成综合与逻辑映射

3. 生成详细 PPA 报告

4. 支持切换不同架构模板或加入自定义功能块(FCB)

5. 输出可用于 SoC 仿真与硬件测试的 Bitstream

该流程已在多家 MCU / AI SoC / 工控芯片客户中成功部署,显著缩短 eFPGA 项目开发周期。

ArkAngel®架构探索与开发流程(Demo)

以下视频展示 ArkAngel® 在架构规划、Floorplan、AI-辅助优化以及应用编译流程中的关键能力。

ArkAngel® 架构探索流程演示:快速floorplan

ArkAngel® 架构探索流程演示:性能评估

ArkAngel® 架构探索流程演示:调整逻辑资源数量

ArkAngel® 架构探索流程演示:调整I/O数量

ArkAngel®开发应用流程演示