在电机控制、数字电源、储能与工业驱动等强实时场景中,ADC采样只是起点,真正决定闭环稳定性与保护响应速度的是采样之后的“后处理链路”——偏移补偿、误差运算、窗口比较、过零检测以及与ePWM/故障引脚的硬件联动。

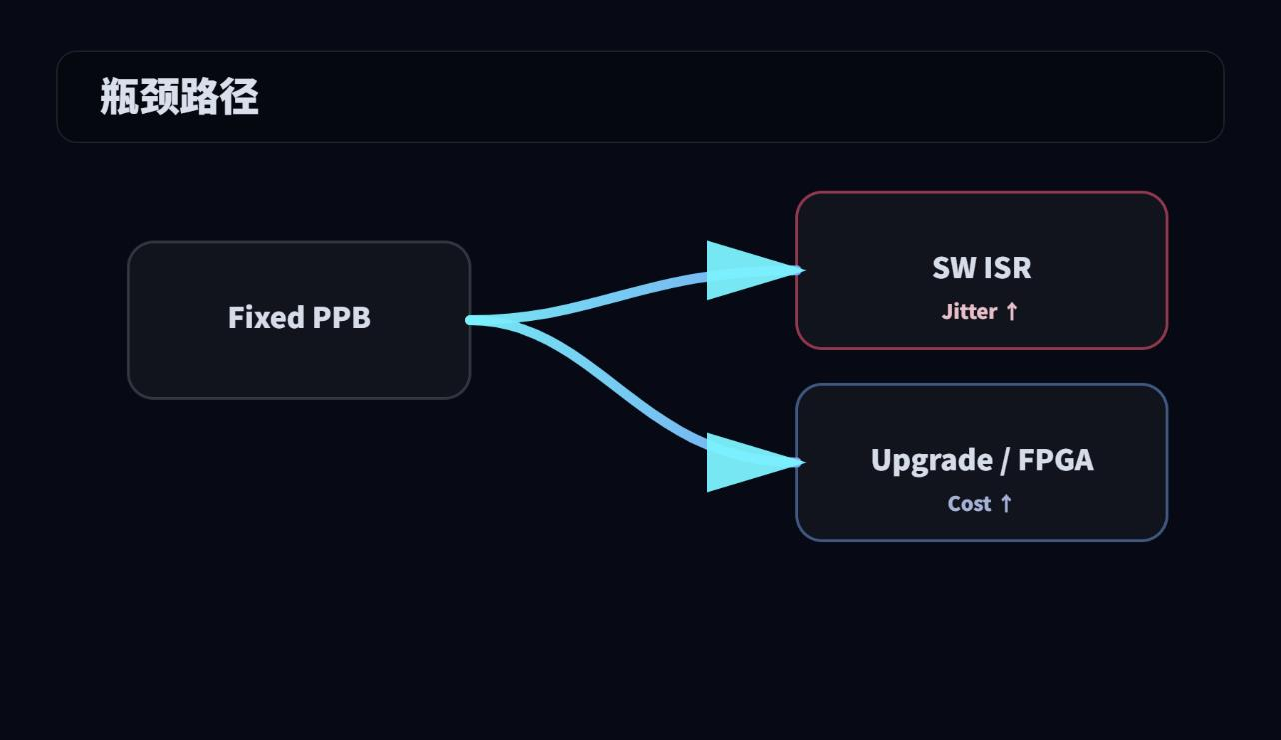

以TI C2000为代表的MCU内置PPB能以近乎零CPU开销完成标准功能,但当系统需要更复杂的数字滤波、工况相关补偿与更细粒度的保护策略时,固定硬件的扩展上限会迫使方案转向ISR软件处理(引入延迟与抖动)或 升级/外挂器件(抬升成本与周期)。

DSA(Domain Specific Area)eFPGA通过在系统中提供面向ADC后处理的可编程硬件域,把“关键路径仍在硬件”的确定性与“功能可迭代”的灵活性结合起来,使PPB从固定模块升级为可持续演进的平台能力。

一、PPB 是什么?

PPB(Post-Processing Blocks)位于“ADC 结果”与“控制/保护动作”之间,承担硬件级后处理: 把偏移校准、误差计算、阈值比较、过零检测等高频 、动作放在硬件路径上,减少CPU参与,从而获得更短且更确定的响应延迟。 在高PWM频率、多通道采样、强实时保护的系统里,这条链路往往比“更高算力”更关键。

PPB 在链路中的位置:ADC 输出→硬件后处理→事件联动,缩短保护路径。

以市场上广泛应用的 TI C2000 为例,其PPB主要覆盖如下典型功能:

• 结果校准/偏移补偿:对ADC转换结果做硬件偏移校正,减小零漂、去偏置。

• 结果运算:与参考值相减得到误差;支持两补表示双极性。

• 硬件比较与检测:高/低阈值窗口比较(Trip High/Low)、零点穿越 (Zero-cross)。

• 事件/中断联动:比较/过零结果可直接产生事件/中断,并通过硬件通路 联动 ePWM/引脚实现快速保护。

二、PPB 的作用

PPB 的价值之一是把常见后处理固化为“寄存器配置 + 硬件自动执行”。例如偏移校正场景: 将 PPB 配置到所需 SOC(采样触发),并把偏移校正值写入OFFCAL寄存器后,PPB会自动对原始结果加/减OFFCAL并写入结果寄存器。 在12 位/16位模式下,还会对结果进行饱和处理(分别限制到 0~4095 或 0~65535)。

硬件饱和逻辑的工程意义

偏移校正后的结果可能出现负值或超量程值。PPB通过硬件饱和把结果限制在合法码值范围内, 避免软件额外做裁剪与异常分支,从而降低ISR路径的抖动风险。

痛点:固定PPB的优势来自“硬件自动路径”,但也意味着扩展能力受限。

三、现有方案的瓶颈

当系统需要更复杂的数字滤波、更精细的工况相关补偿、更复杂的保护判据时,固定PPB往往无法覆盖, 需求会被迫转移到软件或更高端平台,带来抖动、CPU占用、成本与交付周期压力。

• 灵活性不足:滤波/补偿/检测策略难以扩展。

• 软件介入抖动:ISR 竞争与负载变化导致保护延迟不可预测。

• 成本路径变陡:升级MCU或外挂FPGA/CPLD,BOM与验证成本上升。

瓶颈聚焦:功能固定→需软件补足;

换型/外挂→成本与开发周期上升。

四、DSA eFPGA如何破局

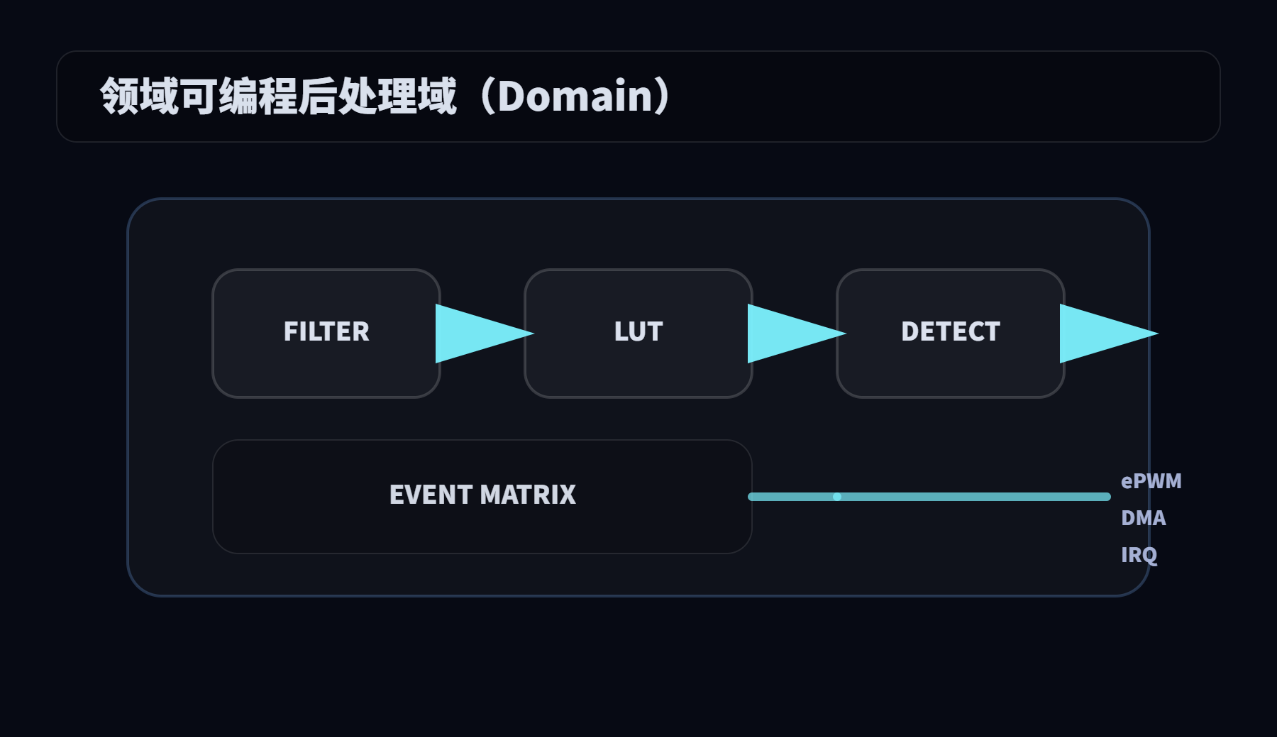

DSA(Domain Specific Area)eFPGA的思路不是用通用FPGA取代MCU, 而是在系统中提供一块面向后处理的可编程硬件域: 专注覆盖ADC后处理、 滤波、补偿、比较检测与事件联动。它的价值是:关键路径走硬件,策略可迭代。

• 可编程滤波:FIR/IIR/陷波/移动平均/去毛刺等按项目组合。

• 可升级补偿:LUT、分段线性、温漂/工况相关系数切换。

• 可组合检测:窗口+迟滞+时间门限、过零消抖、动态阈值。

• 硬件事件矩阵:直连ePWM Trip/GPIO/IRQ/DMA,缩短保护链路。

关键对比:把“µs 级(软件)”的链路拉回“ns 级(硬件)”

当固定PPB能力不足而转向ISR/DSP时,响应常落在µs级并伴随抖动。 DSA eFPGA用硬件流水线承接升级后的后处理,在100–300MHz时钟下, 10–50个cycle对应几十~几百 ns固定延迟(具体与实现有关)。

因此,硬件确定性是保护链路的关键指标。

五、方案横向对比

对比维度包括工具复杂度、成本与性能确定性。对比内容仅用于体现趋势;实际需结合目标器件实测。

维度 | 固定 PPB(TI C2000 等) | DSA eFPGA(领域可编程) | 外挂通用 FPGA/CPLD |

工具复杂度 | 低:MCU IDE + 外设配置 | 中:eFPGA 相关配置工具嵌入在芯片整体开发软件中 | 高:独立开发工具,需单独开发 |

灵活性 | 固定功能,上限明显 | 高:滤波/补偿/比较 /事件可重构 | 高,但常“过重” |

延迟确定性 | 硬件路径确定;超出后上软件→抖动 | 硬件流水线:延迟固定,抖动≈0 | 内核确定,但跨芯片接口增加复杂度 |

成本路径 | 起点低;不足时常要升型号 | 折中最优:按域定制,避免大幅升级 MCU | 通常最高:额外芯片+电源+PCB+验证 |

关键指标 | 复杂后处理进 ISR:µs 级且有抖动 | 100–300MHz 下 10–50cycle:几十~几百 ns | 逻辑快,但集成/验证周期长 |

由上可看出,DSA eFPGA在可编程性与成本/复杂度之间更均衡。

六、芯璐科技的DSA eFPGA产品

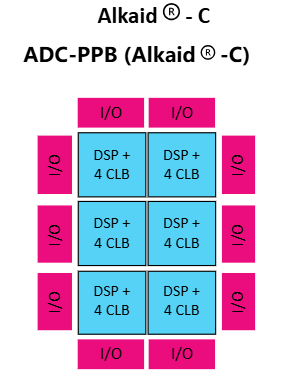

面向 ADC PPB 后处理与工业控制的强实时需求,上海芯璐科技有限公司 (Rapid Flex)已推出相应的DSA eFPGA产品与配套方案 —— MX200e AlkaidC系列, 以“领域可编程后处理域”的方式,帮助客户在不显著抬升系统复杂度与成本的前提下,获得更强的可定制能力与确定性性能。

该系列的主要特色有:

• 面向 PPB 的组件化能力:滤波、补偿、比较、过零、事件矩阵等可组合。

• 更短的保护通路:硬件联动 ePWM/GPIO/IRQ/DMA,减少软件介入。

• 更好的平台复用:同一硬件平台支持多客户策略差异化,提升迭代效率。

项目 | 说明 |

标准版配置 | 300 个 LUT + DSP |

关键收益 | 在不增加外挂 FPGA 系统成本的前提下,将关键后处 理/保护链路的端到端响应从10µs级降至ns级,并实现近零抖动的确定性实时控制。 |

架构特点 | 通过将领域 IP 深度嵌入 eFPGA Fabric并以硬件流水线与事件矩阵直连 ePWM/IRQ/DMA,实现最短互联 与最高效数据交互,从而获得极低延迟与高可扩展性。 |

可定制性 | LUT 规模及Hard IP数量可按客户需求定制,满足PPA目标 |

MX200e AlkaidC 系列架构示意图:

芯璐科技面向ADC后处理领域推出的DSA eFPGA方案在“ADC 后处理与快速保护链路”这一类强实时场景中具备显著优势:

1. 性价比极致:通过将关键后处理/保护决策路径硬件化,并结合领域专用Hard IP加速,实现更低资源占用与更短响应延迟,使系统在满足纳秒级确定性需求的同时,将整体成本压到更优区间。

2. 灵活可扩展:支持可配置的LUT规模与Hard IP组合,芯片设计者可针对不同复杂度的电机应用(通道数、滤波强度、保护策略颗粒度)裁剪出“最经济的域配置”,避免为了少数功能被迫升级MCU或外挂FPGA。

3. 开发高效:依托成熟的EDA工具链与预置领域IP/参考设计,显著降低集成门槛与验证复杂度,让“后处理策略的迭代”从改硬件变成可控的配置/综合流程,从而缩短开发周期并加速产品上市。

4. 国产领先与自主可控:作为国内首批eFPGA IP提供商之一,芯璐科技为国内驱动芯片设计企业提供了先进、可靠且可持续演进的关键技术路径,降低供应链与技术受制风险。

通过采用芯璐科技的eFPGA解决方案,主芯片厂商能够构建真正兼具高性能、高灵活性与长生命周期的下一代控制芯片平台,使后处理与快速保护能力随产品路线持续演进。

七、总结

DSA(Domain Specific Area)eFPGA 的价值在于:在不引入外挂FPGA系统成本与开发负担的前提下,将PPB从固定模块升级为“可演进的后处理硬件域”,以硬件流水线与可编程域能力同时满足确定性实时性与长期可迭代性。 从长期产品路线看,eFPGA + MCU/SoC的协同架构将成为更合理的平台化选择——既能跑得快、又能改得动,从而显著延长控制芯片的产品生命周期与商业价值。