在工业自动化、机器人、电机驱动、汽车电子与能源系统等实时控制场景中,系统设计正面临同一个核心矛盾:既要硬件级的确定性低延迟,又要软件级的快速迭代与可升级。

传统做法往往是“MCU/MPU/SoC+外挂独立FPGA”,用FPGA的并行与可重构能力补齐性能与时序确定性;但随着控制频率提升、节点小型化与能效要求提高,片间通信的延迟/抖动、功耗与体积逐渐成为瓶颈。

eFPGA(embeddedFPGA)的出现,本质上是把可编程逻辑从“板级外挂”提升到“芯片级集成”,让可编程硬件与处理器、存储和外设实现“零距离协同”。

传统FPGA(Field-ProgrammableGateArray)是一颗独立的可编程半导体器件,内部由可配置逻辑块(CLB)、片上存储(BRAM)、DSP、以及高速接口等资源组成,可通过编程在硬件层面实现各种数字电路功能,例如协议处理、状态机、并行计算、控制逻辑加速等。

它的优势在于:

· 高度灵活:同一颗FPGA可适配不同项目与不同协议

· 强并行与确定性:适合硬实时状态机与时序敏感逻辑

· 硬件可重构:便于后期功能升级

但作为独立芯片,它必须通过封装引脚与PCB走线连接MCU/SoC,片间互联会引入额外的:

· 延迟与抖动(协议开销、时钟域跨越、驱动与软件栈)

· 功耗(尤其是片外IO驱动与终端匹配)

· 板级面积与BOM成本(更多器件、电源树、布线复杂度)

在实时控制系统中,很多时候“限制性能的不是FPGA逻辑本身”,而是CPU与FPGA之间交换数据的代价。

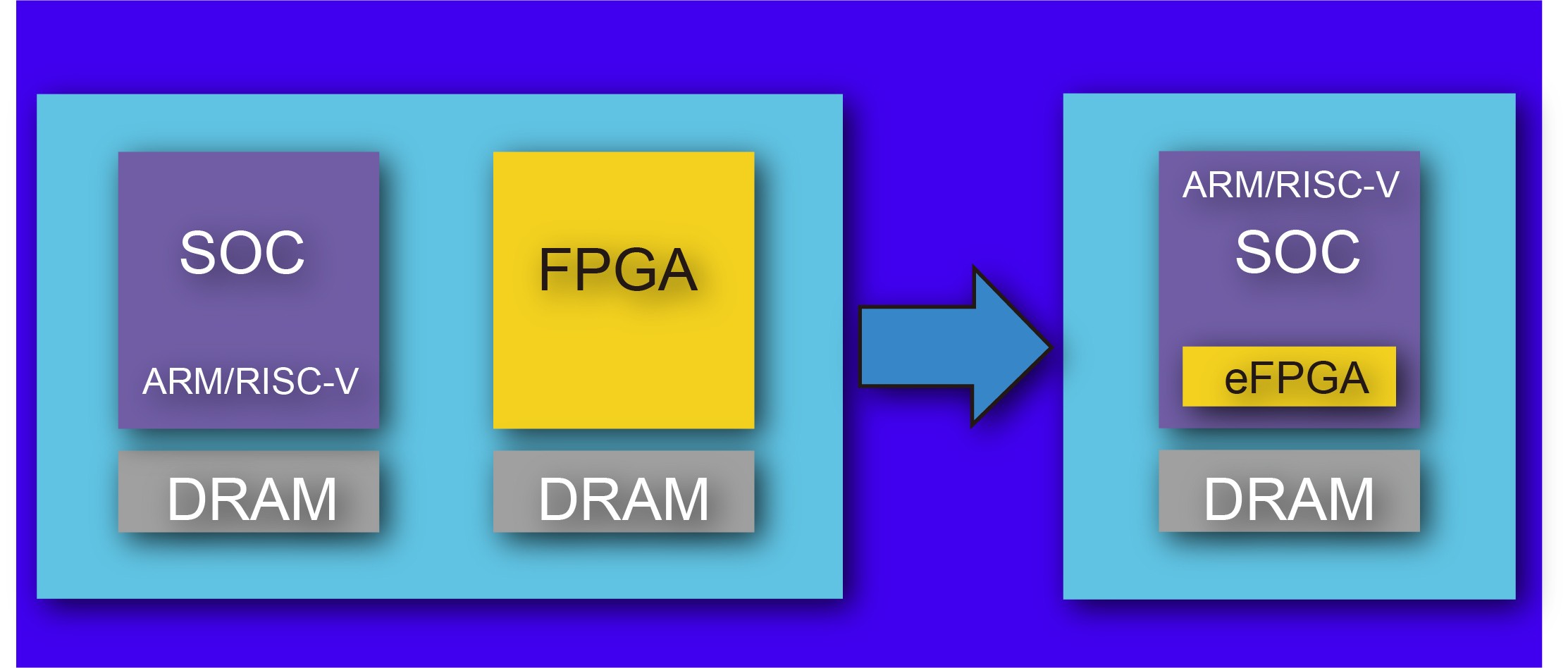

eFPGA(嵌入式FPGA)并不是一颗独立芯片,而是一种IP核:芯片设计师可以像集成CPU核、SRAM或外设一样,将一块可编程逻辑阵列直接集成到SoC的硅片内部,并通过片内互联(如AMBA/AXI/AHB等)与处理器核心、DMA、存储器与外设直接通信。

如下图所示:

因此,eFPGA的关键价值在于:

· 把可编程能力“嵌入”SoC,形成片内直连

· 将通信从“跨封装/跨PCB”变成“片内总线级数据交换”

· 将系统实时性、功耗和集成度提升到新的层级

一句话概括:传统FPGA是“外接的硬件加速器”,eFPGA是“片内可重构硬件单元”。

维度 | 传统独立FPGA | eFPGA(嵌入式FPGA) |

形态 | 独立物理芯片 | SoC内部IP核 |

互联 | 引脚+PCB+外部协议 | 片内总线直连(AXI/AHB等) |

延迟/抖动 | 片间交互多为µs级,抖动源多 | 片内交互可到ns级,抖动更可控 |

功耗 | 片外IO驱动与终端开销显著 | 消除大部分片外IO开销,功耗更低 |

板级面积/BOM | 需要额外芯片与外围器件 | 节省PCB、减少外围器件 |

灵活性 | 通用型强 | 可按目标场景定制规模/资源 |

4. eFPGA相较传统独立FPGA的优势

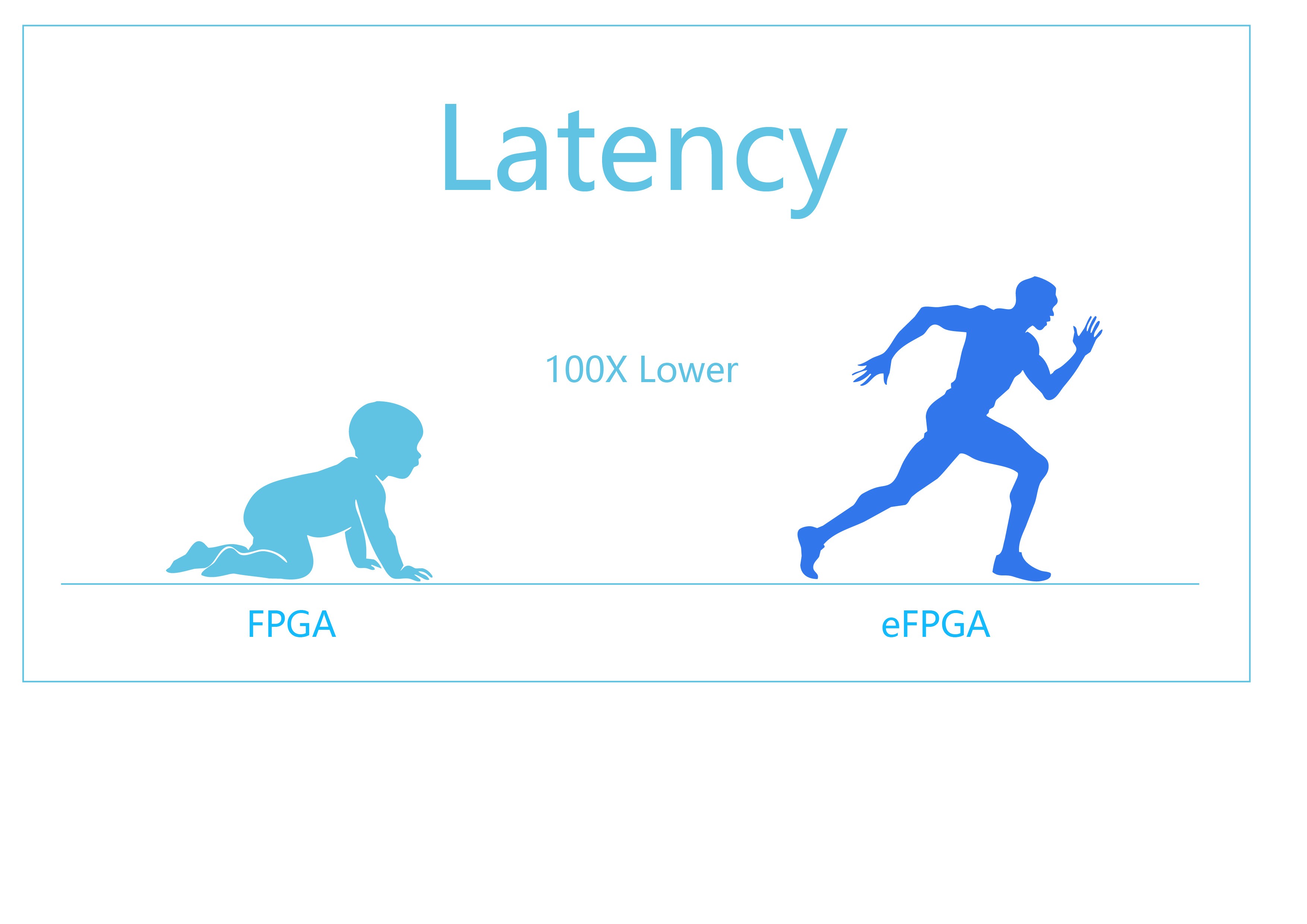

控制系统的核心指标往往是闭环延迟与抖动(jitter)。

传统外接FPGA:MCU/SoC↔FPGA

· 使用SPI或类似外设接口时,单次事务(含协议/等待/片选/驱动开销)常见1–10µs量级;复杂驱动栈与任务调度会进一步放大抖动。

· 使用并口可以缩短延迟,但往往要付出引脚与布线成本。

· 使用PCIe/SerDes虽吞吐高,但系统级往返(DMA/中断/协议层)在控制响应上仍常见数µs级,并带来更多抖动来源。

eFPGA:CPU/DMA/外设↔eFPGA(片内AXI/NoC)

· 片内互联事务延迟通常在几十ns–数百ns(与总线结构/频率相关)。

· 若将关键控制路径(例如PWM更新触发、编码器计数、硬件状态机)直接放入eFPGA并靠近外设寄存器,很多“事件到动作”的路径可收敛到10–100ns级(少量时钟周期)。

由此可见:在大量实时控制链路中,eFPGA可将“通信相关延迟”从µs级压缩到100ns级甚至更低,带来10×–100×的数量级改善,并显著降低抖动源,使系统更容易达成硬实时指标。

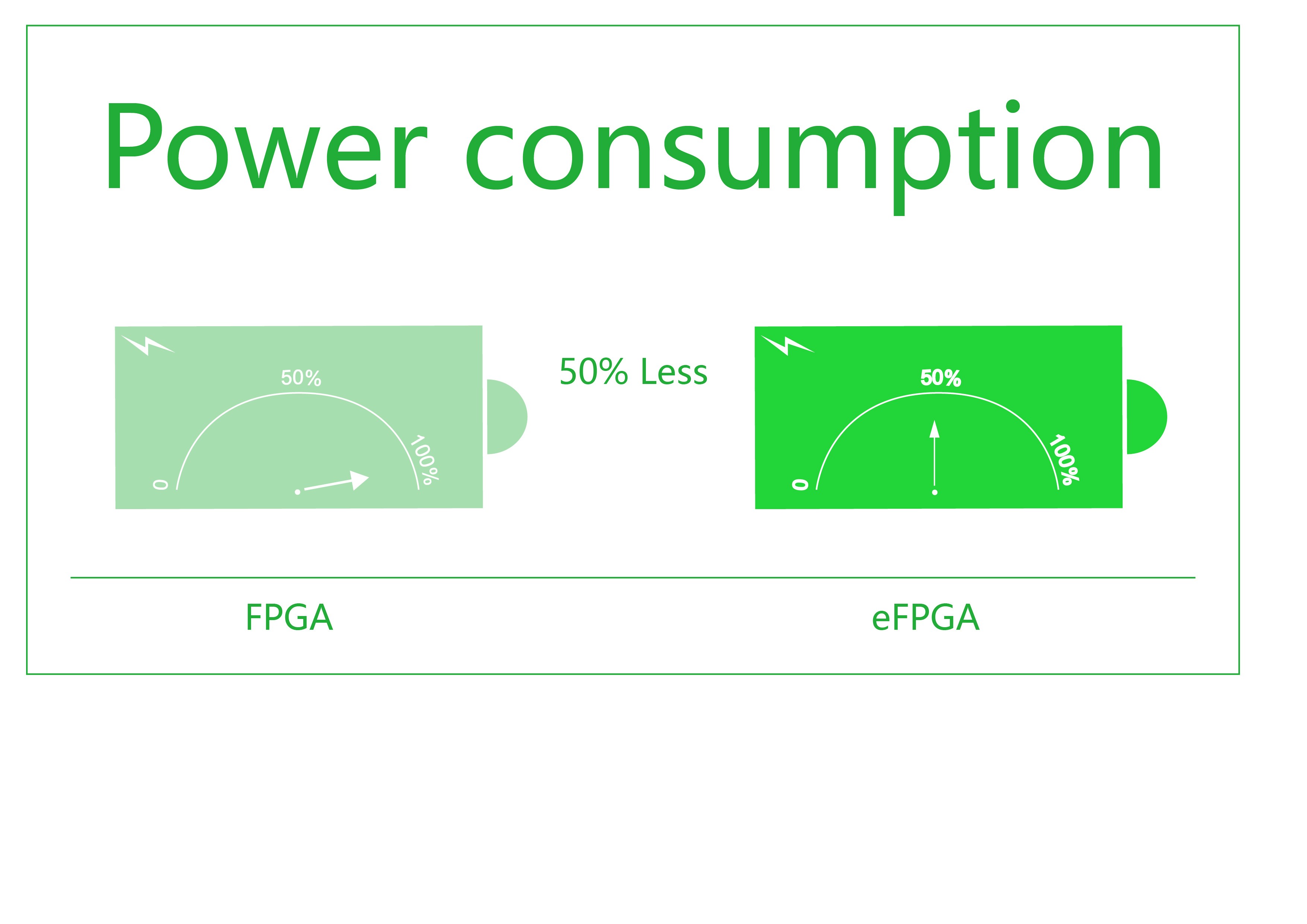

外接FPGA方案中,片外IO(高速翻转、终端匹配、电平转换、驱动能力)往往是高功耗来源之一。

· 在需要持续交换采样/位置/状态量的控制系统里,仅“板级互联+IO驱动”带来的功耗就可能达到几百mW到数W(与速率、摆幅、终端方式强相关)。

· eFPGA通过片内互联让数据“不出芯片”,通常可带来:

o 互联相关功耗降低30%–70%(当原系统片外通信占比较高时更明显)

o 以系统视角,常见具有0.2–2W量级的节能空间(依原接口类型与数据交换强度而定)

对长期运行的工业控制、车载控制与边缘节点而言,这往往意味着更低的散热要求、更小的电源设计压力与更高的系统可靠性。

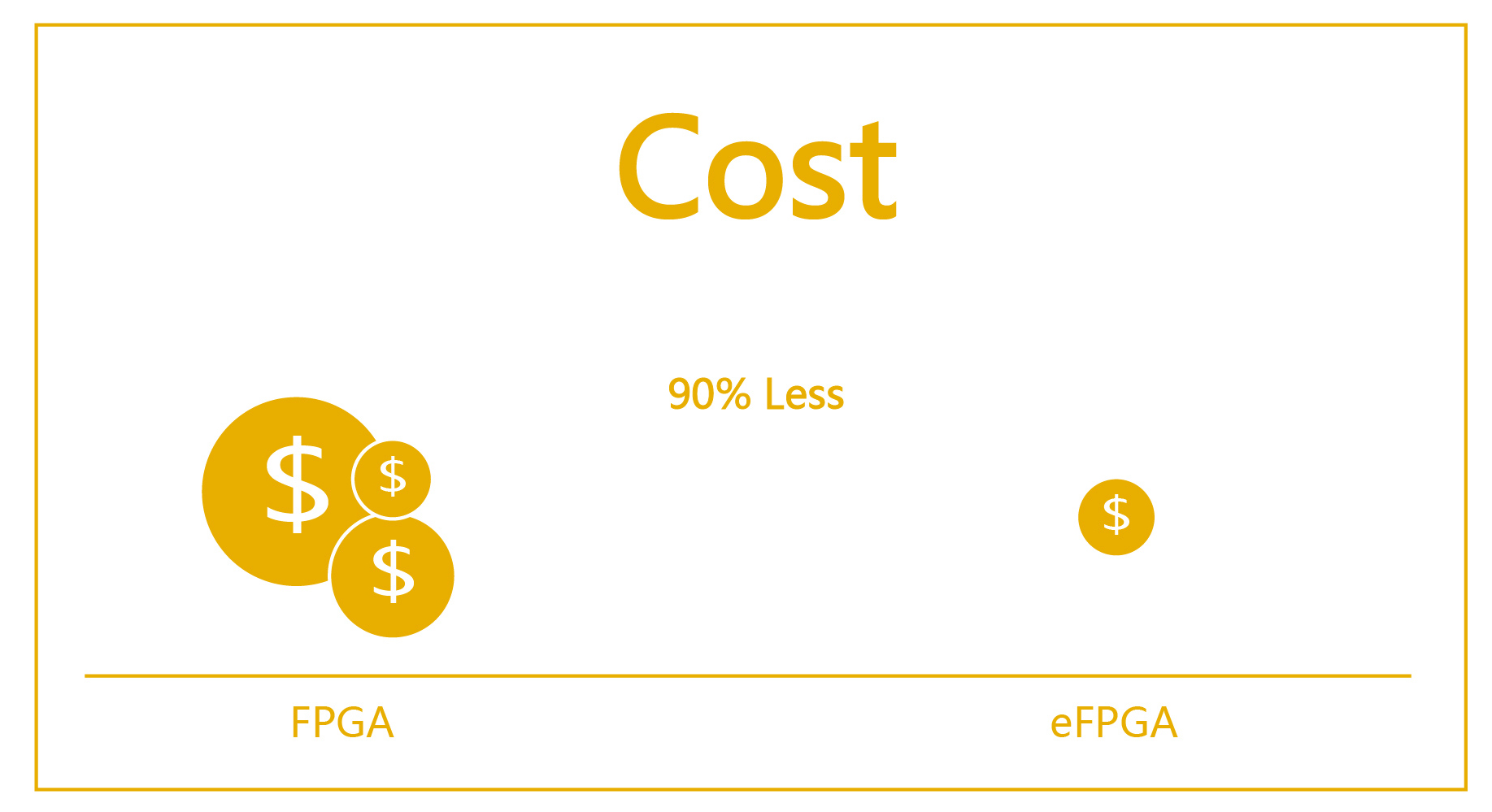

外接FPGA不仅是一颗芯片,还通常伴随:配置Flash(视方案)、额外电源轨与电感电容、时钟器件、接口收发器/电平转换、终端与匹配器件,以及更高的PCB层数与布线复杂度。

采用eFPGA集成SoC后,常见可以实现:

· PCB面积减少20%–50%(取决于原FPGA封装、接口复杂度与电源/走线占比)

· BOM器件数减少5–30颗(电源树、时钟、收发器、Flash、匹配器件等视设计而定)

· 高频信号跨板走线减少,EMI风险与整改成本同步下降

需要强调的是:虽然eFPGA会增加SoC内部硅面积,但对系统交付而言,更直接的收益体现在板级空间、BOM与制造复杂度。

实时控制不仅看峰值带宽,更关注“稳定吞吐+可预测延迟”。

· 板级互联受限于引脚数量、协议与信号完整性:例如SPI常见有效吞吐为几十到数百Mb/s,并口提高吞吐但成本高。

· eFPGA通过AXI/NoC等片内通路,单通道即可提供数GB/s级潜在带宽(取决于位宽与频率),并避免跨封装/跨PCB的不确定因素。

因此在需要高频交换多通道控制数据的系统中,eFPGA更容易实现“高带宽+低抖动”的组合。

综上所述,eFPGA在未来市场的竞争力主要体现在四个方面:

· 确定性更强:片内互联将关键交互从µs拉到ns级,抖动更可控,适合高频闭环、多轴同步等场景。

· 能效更好:减少片外IO与板级互联,带来可观的系统功耗下降空间。

· 集成度更高:减少器件与走线,缩小体积、降低BOM与制造复杂度,提高可靠性。

· 可演进性更强:保留可重构优势,让协议、算法与产品差异化可以在“硬件级”持续升级,而不必频繁更换硬件平台。

传统独立FPGA依然适用于通用开发与需要大规模逻辑资源的场景;但对未来的细分领域,如实时控制领域而言,系统竞争力越来越取决于端到端时延、确定性、能效与集成度。eFPGA通过片内融合把可编程硬件真正变成SoC的一部分,使关键控制路径获得10×–100×的通信延迟改善、显著的功耗与体积优化,并为长期演进提供更好的平台基础。