2025 年 12 月 —— 芯璐科技正式发布ArkAngel Engineering Edition® (AAEE) 全新演示 Demo,全面展示ArkAngel在架构探索(Architecture Exploration)与应用开发(Application Development) 两大领域的完整流程能力。

此次更新将芯璐多年积累的 eFPGA 架构数据库与 AI 推断技术深度结合,使得 eFPGA 的规划、验证与优化效率进一步提升,标志着eFPGA工具链进入“AI 辅助架构设计”的新阶段。

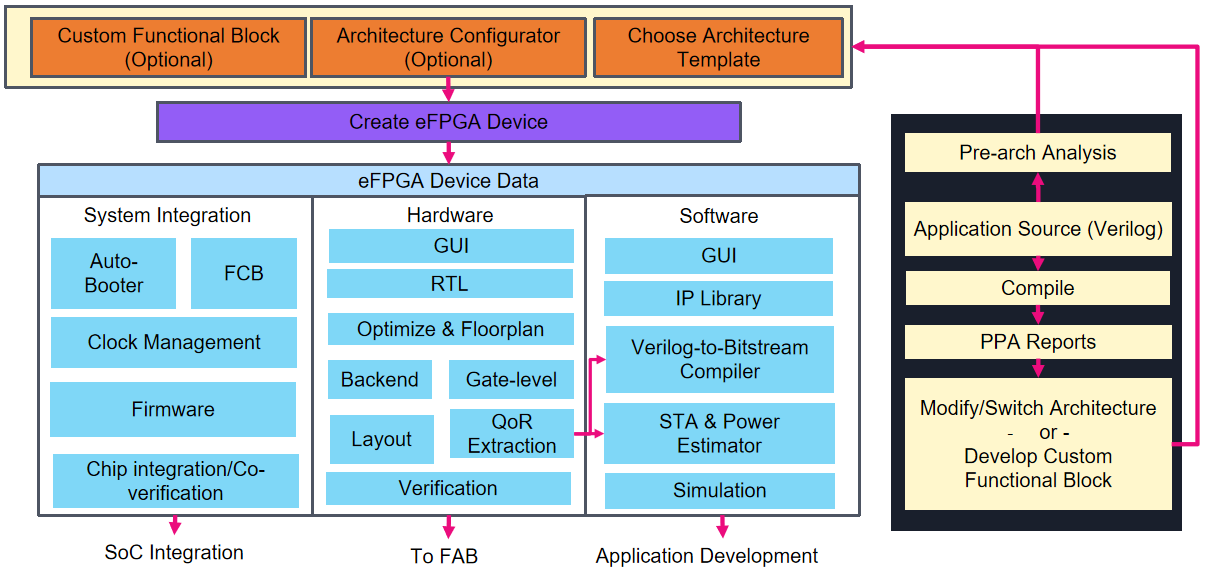

ArkAngel Engineering Edition (AAEE) Eco-System

ArkAngel® 架构探索流程:更快、更准、更智能

在最新 Demo 中,AAEE通过可视化流程展示从前期架构评估到创建 eFPGA 设备模板,再到Floorplan与QoR分析的一体化能力,包括:

1. 快速 Floorplan 与资源规划

用户可在 GUI 中快速调整逻辑资源规模(LUT、寄存器、DSP-lite、BRAM/分布式存储等),并实时查看布局变化,为芯片面积与资源利用率提供直观参考。

2. I/O 资源快速配置

支持灵活调整 I/O 数量、接口组织结构及其与 Fabric 的拓扑关系,为 SoC 集成提供最佳的封装与布线策略。

3. AI 加持的架构探索推断引擎

通过对大量内部 eFPGA 项目的架构数据进行模型训练,AAEE现可在秒级完成如下推断:

· eFPGA 布通率(routability)趋势预测

· 初步逻辑—布线拥塞分析

· Critical path 热区定位建议

· 优化资源结构后的性能预估

在已有验证项目中,基于AI的架构初步优化可令布线结构更均衡,使潜在性能提升达到 20% 以上。

ArkAngel® 应用开发流程:从Verilog到Bitstream的一站式体验

应用开发流程的完整链路:

1. 输入应用源码(Verilog)

2. ArkAngel® 编译器进行综合与映射

3. 生成 PPA 报告(性能 / 功耗 / 面积)

4. 必要时切换不同架构模板或加入 Custom Functional Block

5. 最终生成 Bitstream,进行仿真与系统集成验证

这套流程使开发者能够像使用 ASIC 工具链一样,有结构化、有反馈、有迭代地完成 eFPGA 应用优化,同时保持可重构逻辑的快速迭代优势。

AAEE Eco-System:开放、可扩展、自主可配置

新版Demo强调了AAEE的“可开发性”理念:

· 用户可基于芯璐的模板库创建自己的 eFPGA 架构版本

· 也可定制 Fabric 拓扑、Routing 结构、局部逻辑簇、BRAM 组织等

· 同时支持添加自定义的 FCB(Functional Custom Block),轻松把客户自有 DSA 功能纳入 eFPGA 编译流

AAEE 的目标是让芯片设计者不仅能用 eFPGA,更能 “设计属于自己的 eFPGA”。

芯璐科技:持续推动eFPGA的架构化与智能化

ArkAngel®与AAEE的最新演示,展示了芯璐在智能架构生成、AI 辅助布线预测和敏捷验证等方向的领先能力。

我们相信,未来的eFPGA不再只是可重构逻辑,而是SoC的“可演化算力层”,可根据应用快速迭代、持续升级。

芯璐科技将持续深耕工具链与架构的研发,为合作伙伴提供从架构→软件→物理实现→SoC集成的端到端支持。

ArkAngel® 开发应用流程演示地址:/index/solutions/id/10