2025年5月 · 上海 —— 国内领先的嵌入式FPGA技术提供商芯璐科技今日正式发布其最新设计生态系统平台 AAEE(ArkAngel Engineering Edition),该平台是芯璐自研嵌入式FPGA(eFPGA)架构 ArkAngel 的工程版工具链,目标是构建从架构定义到版图生成的自动化开发流程,是嵌入式FPGA领域的“Xtensa 式”平台化生态的一次跨越式升级。

ArkAngel = FPGA界的Xtensa

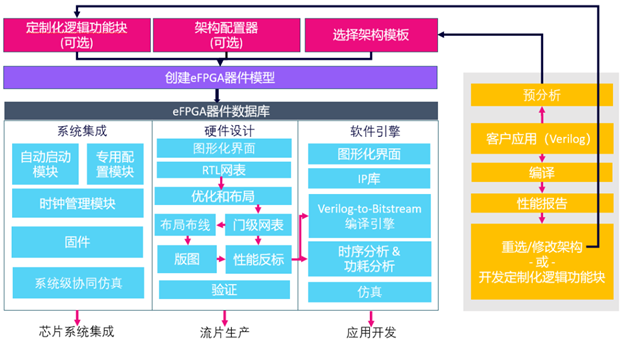

AAEE 提供了一个完整的、可迭代的 eFPGA 设计流程,覆盖软硬件协同开发全路径,包括:

硬件设计自动化:从架构配置、网表生成到物理版图集成,实现一站式流程闭环;

软件编译支持:集成 Verilog-to-Bitstream 编译链,支持自动性能评估与报告生成;

系统集成模块:通过丰富的外设 IP 仓库,可快速组合构建完整的 eFPGA 子系统;

图形化界面:全流程可视化支持,让架构设计、资源调配、结果分析一目了然。

“如果 Xtensa 定义了可配置CPU的集成标准,那 ArkAngel 就是在为下一代 SoC 构建可配置的嵌入式FPGA 核心。” —— 芯璐科技CTO唐希凡博士

图示:ArkAngel 生态系统

开发工具链开放可控,兼顾灵活性与工程可靠性

AAEE 平台由一套基于C++与Python的模块化工具链组成,支持:

开源引擎为内核(如Yosys、nextpnr等): yosys, verilog-to-routing, OpenFPGA等

商用生产版许可证控制:满足客户对知识产权与部署可控性的需求

一体化集成支持:与主流RTL仿真工具、EDA后端流程深度兼容

迭代式优化支持:支持跨周期优化、硬件反馈指导软件配置等高级功能

超越Xtensa:软硬协同,实时反标,性能驱动

AAEE 不仅复制了Xtensa的高自动化、配置式开发理念,更在以下维度实现突破:

软硬件互动设计:实时获取仿真/综合反馈,优化架构参数

智能化后端优化:提供包括路径调优、功耗感知布图等优化机制

可插拔式架构插件机制:支持快速集成客户自定义资源模块

支持性能需求驱动的目标反推(constraint-driven synthesis)

eFPGA 未来的开发范式:平台+IP+生态

AAEE 同时也集成了芯璐科技最新一代嵌入式FPGA不同架构,其中 AlkaidC架构具备:

面积仅为 0.26 mm²(post-shrink)

LUT: 96,FF: 192,Pcounter:24

定位于电机控制、MCU协同计算等边缘智能领域

对标TI C2000系列,适配主流M4 MCU生态

应用场景与客户价值

AAEE+AlkaidC 的组合已在以下场景落地:

微型电机控制器(MCU + eFPGA)

工业自动化控制模块(实时逻辑可重构)

ASIC SoC内集成可配置计算模块

教学/科研领域的自定义架构实验平台

关于芯璐科技

芯璐科技专注于新一代嵌入式FPGA架构与工具链的自主研发,是国内少数具备从架构设计到部署工具链全栈能力的芯片设计公司。AAEE的发布标志着芯璐科技正式进入IP+平台双轮驱动模式,为国产定制化FPGA设计产业提供一条新的技术路径。